## 9. Voltage references

A voltage and current reference are used for the reference of bias circuit, DAC and ADC.

Kanazawa University Microelectronics Research Lab. Akio Kitagawa

### 9.1 Simple reference circuits

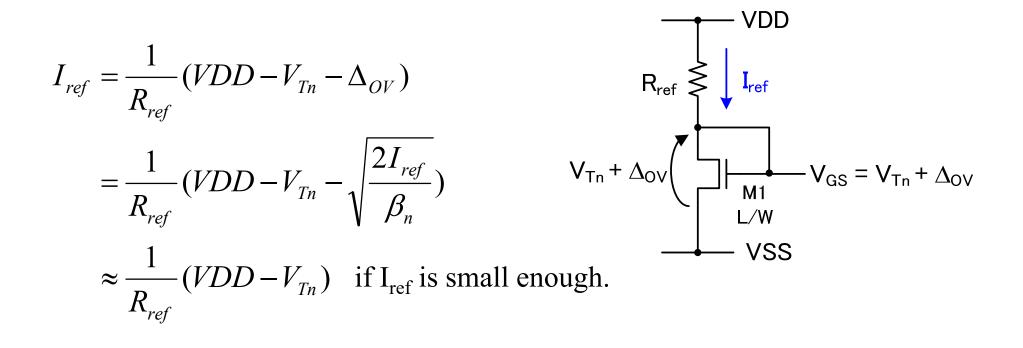

#### **R-MOSFET** voltage reference

- Bad stability against the temperature variation, because the temperature coefficient of  $I_{ref}$  depends on the temperature coefficient of  $R_{ref}$  and  $V_{Tn}+\Delta_{OV}$ .

- No stability against VDD, because  $I_{ref}$  and  $V_{GS}$  depend on VDD.

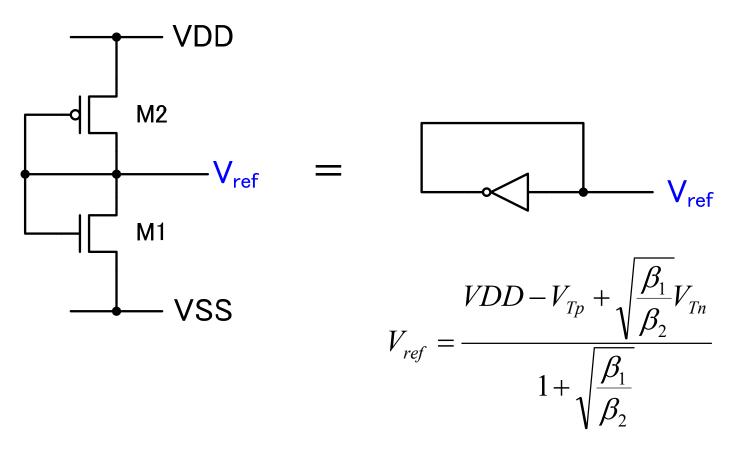

#### **MOSFET** Driver

- No stability against VDD, because V<sub>ref</sub> depends on VDD.

- The temperature coefficient of  $V_{Tn}$ ,  $V_{Tp}$  can be canceled by a temperature coefficient of  $\beta_1/\beta_2$ .

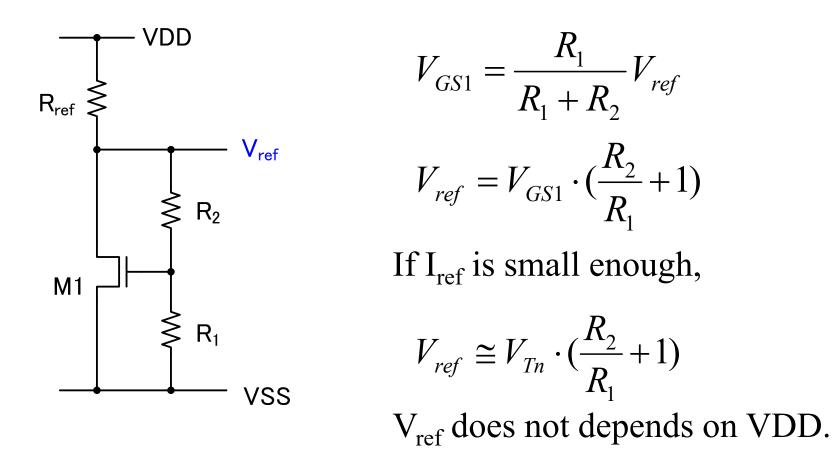

Threshold-Voltage Multiplier This circuit has a NFB loop in which the decrease of  $I_{ref}$  causes the increase of  $V_{GS}$ .

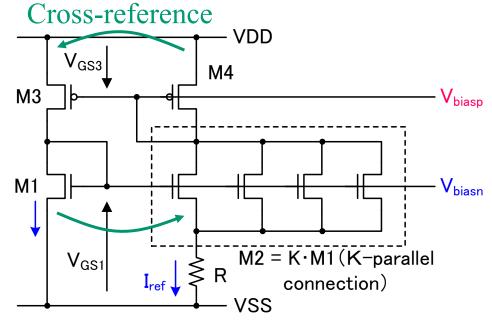

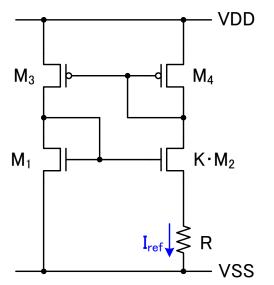

## 9.2 Beta-Multiplier Reference (BMR)

#### Principle of BMR circuit

$$I_{DS1} = \frac{\beta_1}{2} (V_{GS1} - V_{Tn})^2$$

-I -I

I

$$I_{DS2} = \frac{\beta_2}{2} (V_{GS2} - V_{Tn})^2 = K \frac{\beta_1}{2} (V_{GS2} - V_{Tn})^2$$

$$I_{DS1} = I_{DS2} = I_{ref}$$

$$I_{ref} = \frac{1}{R} (V_{GS1} - V_{GS2}) = \frac{1}{R^2} \frac{2}{\beta_1} (1 - \frac{1}{\sqrt{K}})^2 \quad \langle$$

$$\begin{split} \mathbf{V}_{\mathsf{biasp}} & \begin{cases} I_{DS4} = I_{DS3} \\ I_{DS1} = I_{DS2} \equiv I_{ref} \\ V_{GS1} = V_{GS2} + I_{ref} R \\ & \text{i.e.} \\ \beta_2 = \beta_1 \rightarrow I_{ref} R = 0 (V_{GS1} = V_{GS2}) \\ \beta_2 = K \beta_1 \rightarrow I_{ref} R \neq 0 (V_{GS1} = V_{GS2} + I_{ref} R) \\ & (\mathsf{BMR: Beta-Multiplier Reference}) \end{split}$$

$= \begin{array}{l} I_{ref} \text{ is independent on VDD.} \\ \hline \\ \text{The temperature coefficient of} \\ I_{ref} \text{ depends on the temperature} \\ \text{ coefficients of R and } \beta_1. \end{array}$

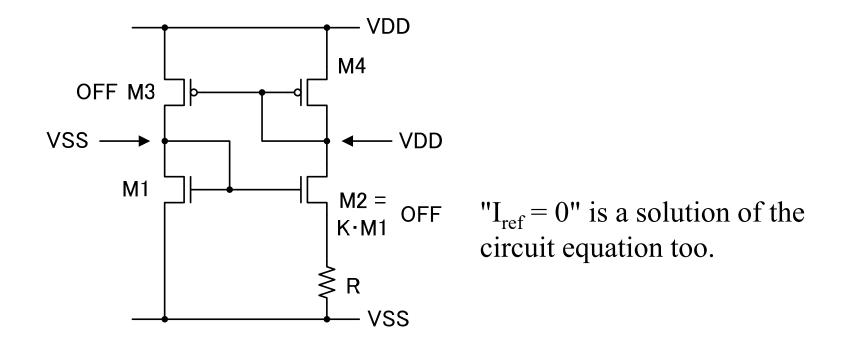

### Start-up circuit (1)

BMR has two operating state because of a positive feedback. □ The initial state should be determined by the start-up circuit.

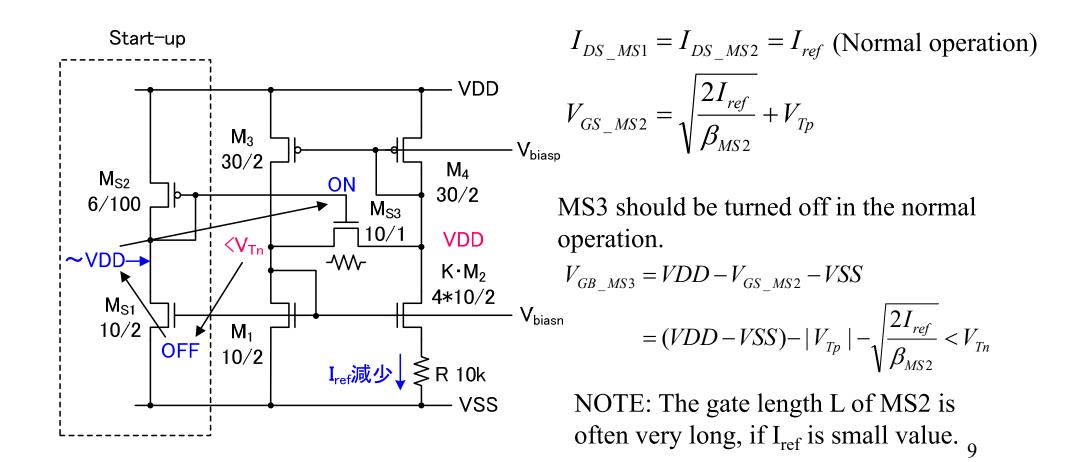

#### Start-up circuit (2)

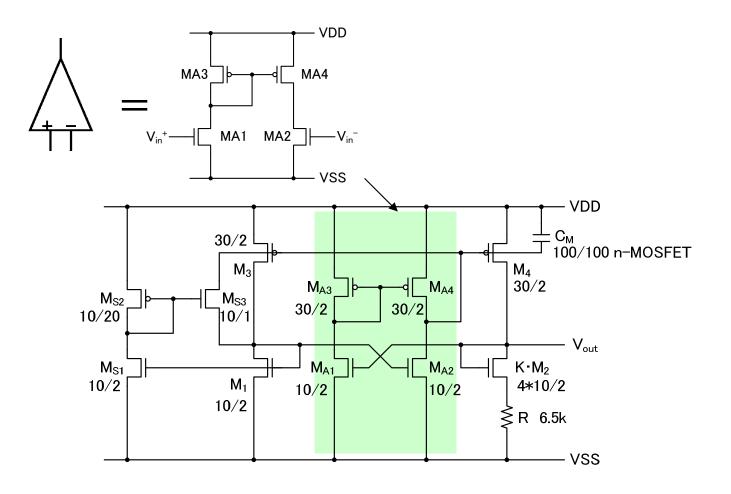

#### The drain potential of M1-M4 is equalized by MS3.

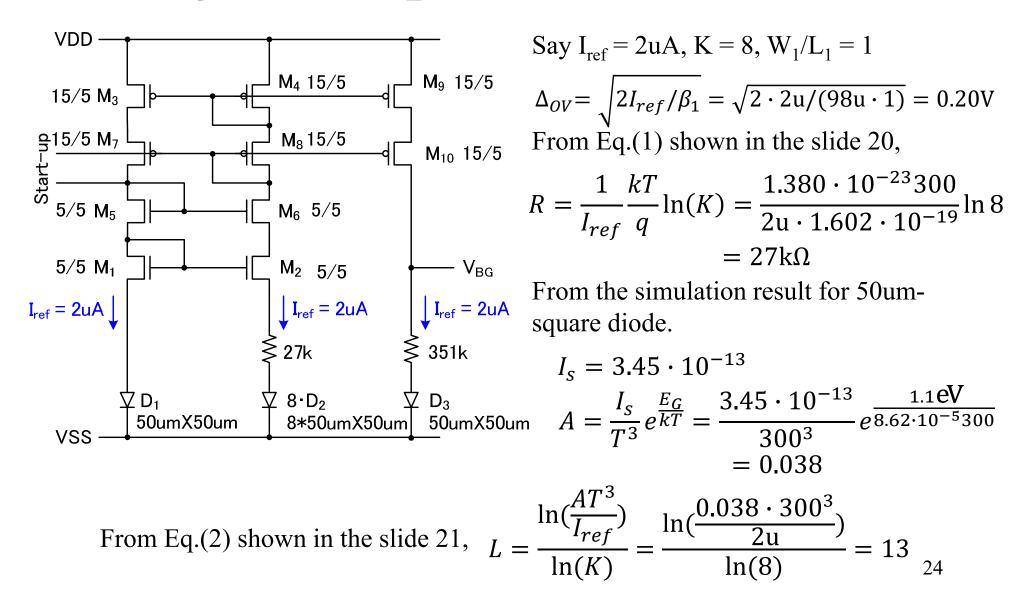

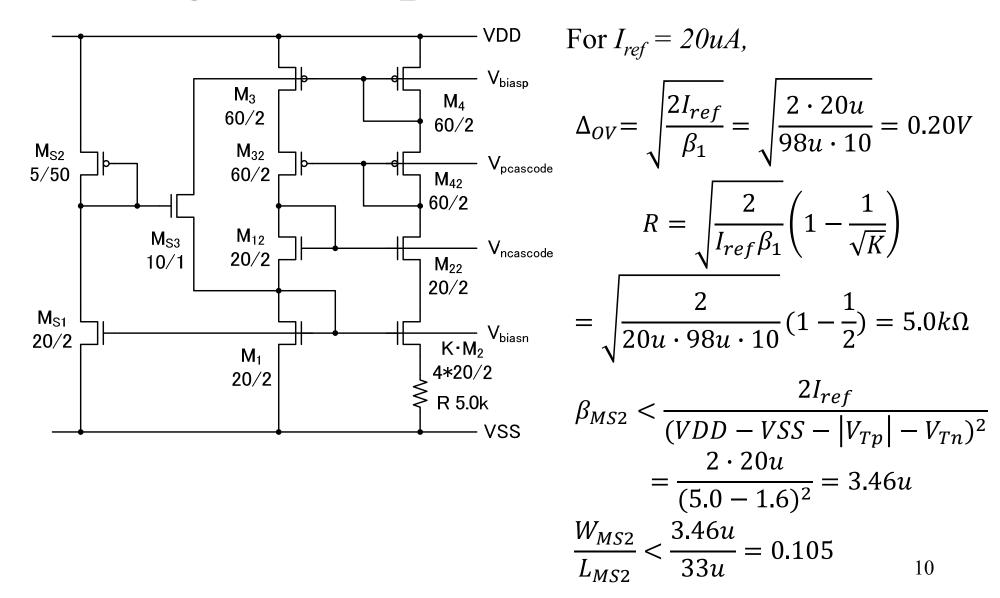

#### Design example of cascode BMR

#### Voltage regulation

# Low-voltage BMR with the voltage regulation

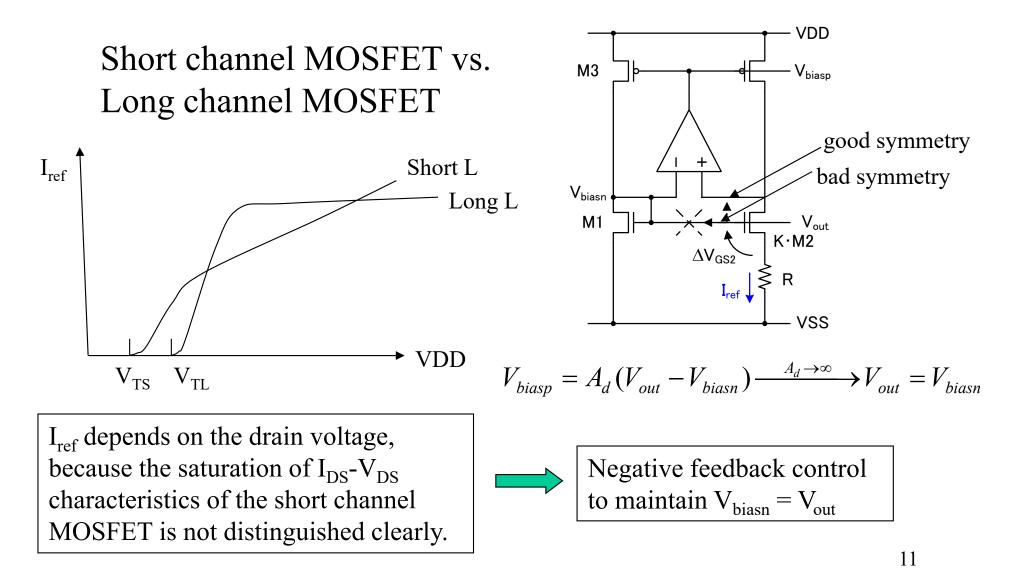

BMR circuit for the short channel MOSFET

12

## Sub-threshold BMR for lowpower circuits

Very low power consumption BMR

The circuit topology is same as the normal BMR.

$I_{DS}$ - $V_{GS}$  characteristic in the sub-threshold region.

$$I_{DS} = \frac{W}{L} I_0 \exp\{\frac{q(V_{GS} - V_T)}{mkT}\}, \quad m = 1 + \frac{C_D}{C_{OX}}$$

$$V_{GS1} = m \frac{kT}{q} \ln(\frac{I_{ref}}{I_0} \frac{L}{W}) + V_{Tn}$$

$$V_{GS2} = m \frac{kT}{q} \ln(\frac{I_{ref}}{I_0} \frac{L}{K \cdot W}) + V_{Tn}$$

$$I_{ref} = \frac{1}{R} (V_{GS1} - V_{GS2})$$

$$= \frac{m}{R} \frac{kT}{q} \ln K$$

NOTE: The very large resistance R is required.

#### 9.3 Band-gap reference (BGR)

It is not easy to cancel the temperature dependence of  $R^2\beta$  in BMR shown in slide 7, because R and MOSFET are fabricated in the different stages of the CMOS process. The temperature coefficient of the reference voltage can be compensated with a pair of pn junctions.

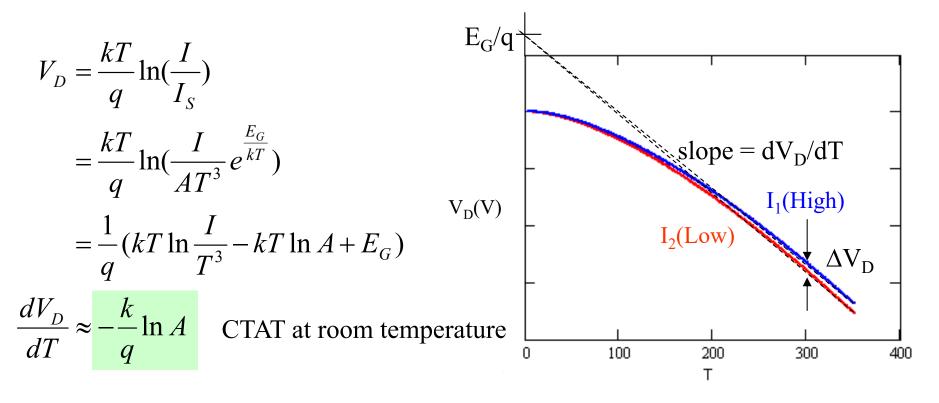

## Temperature dependence of pn junction diode

The temperature coefficient is canceled with pn diode.

DC characteristic of pn junction ----NOTE: Only a diffusion current is modeled in this equation. Therefore, the appropriate bias voltage have to be applied to the pn junction.

$$I = I_{S} (e^{\frac{qV_{D}}{kT}} - 1) \cong I_{S} e^{\frac{qV_{D}}{kT}}$$

$$V_{D} = \frac{kT}{q} \ln(\frac{I}{I_{S}})$$

$$I_{S} = AT^{3} e^{-\frac{E_{G}}{kT}}$$

Is : Reverse saturation current k : Boltzmann constant (8.62E-5 eV/K) T : Absolute temperature (K) q : electron charge (1.60E-19 coulomb)  $E_G$  : Band-gap energy of Si (1.1eV) A : Constant depending on the effective density of state and impurity concentrations

## CTAT (Complementary to absolute temperature)

$V_D$  has a negative temperature coefficient at room temperature.  $\Delta V_D$  has a positive temperature coefficient at room temperature.

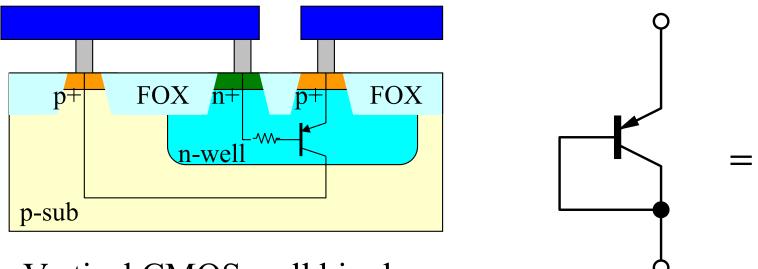

### Structure of the pn junction diode

Vertical CMOS well bipolar junction transistor

Equivalent schematic

The current  $I_B$  should be limited less than 0.1mA to reduce the voltage drop in the base resistance of pnp transistor.

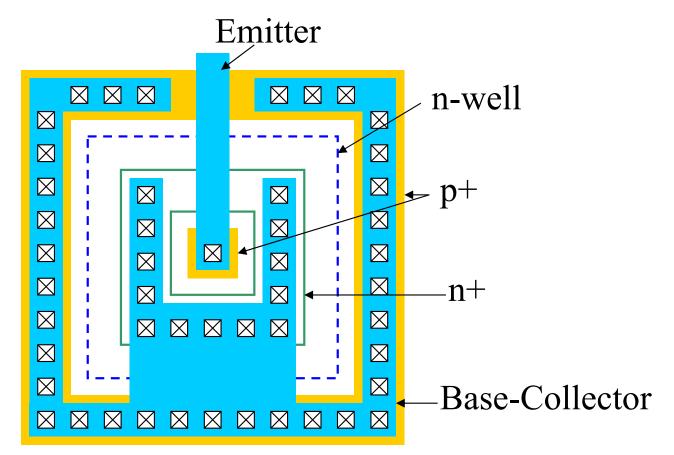

### Layout sample of the pn junction diode

Check the production tolerance of pn junction.

The standard deviation of the I-V characteristics of pn junction is rather smaller than  $V_T$  of MOSFET, but it may not be controlled by the foundry.  $_{18}$

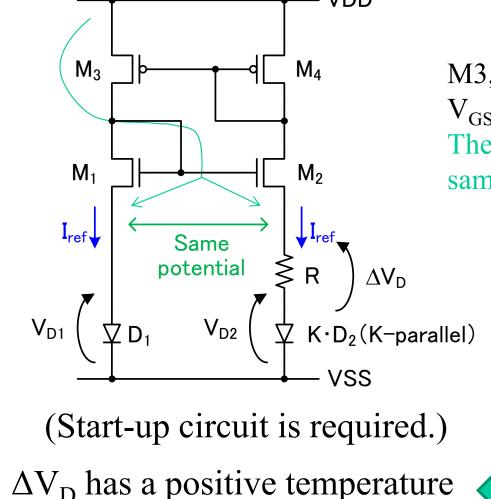

## PTAT (Proportional to absolute temperature)

coefficient

M3, M4: Current mirror.  $V_{GS1} = V_{GS2}$  (because the  $I_{DS1} = I_{DS2}$ ) The source potential of M1 and M2 is same, then  $V_{D1} = V_{D2} + \Delta V_D$

$$\begin{cases} I_{D1} = \frac{1}{K} I_{D2} \\ V_{D1} = \frac{kT}{q} \ln(\frac{I_{ref}}{I_s}) \\ V_{D2} = \frac{kT}{q} \ln(\frac{I_{ref}}{KI_s}) \end{cases}$$

$$\checkmark \Delta V_D = \frac{kT}{q} (\ln \frac{I_{ref}}{I_s} - \ln \frac{I_{ref}}{KI_s}) = \frac{kT}{q} \ln K$$

19

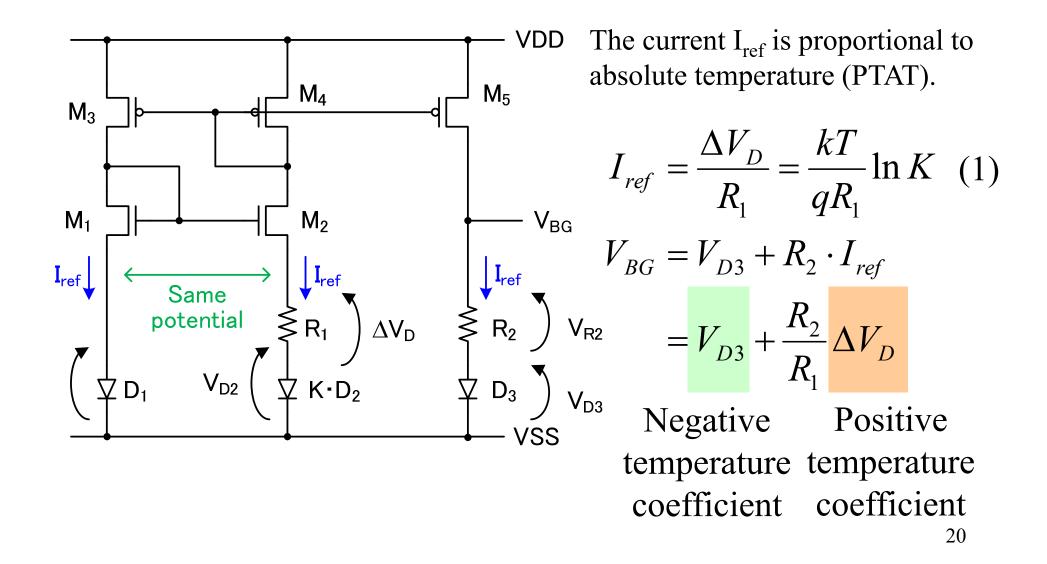

#### BGR voltage reference

## Cancelation of temperature coefficient

$$V_{BG} = V_{D3} + \frac{R_2}{R_1} \Delta V_D$$

=  $\frac{kT}{q} \ln \frac{I_{ref}}{AT^3} + \frac{E_G}{q} + \frac{R_2}{R_1} \frac{kT}{q} \ln K$

=  $\frac{kT}{q} \left(\frac{R_2}{R_1} \ln K - \ln \frac{AT^3}{I_{ref}}\right) + \frac{E_G}{q}$

$\downarrow$

$0$

$\frac{1}{R_2} = \frac{\ln \frac{AT^3}{I_{ref}}}{\ln K} (2)$

Note: The equation (1) is satisfied at the given temperature . You need to measure AT<sup>3</sup> at the operating temperature of the circuit.

Band-gap Reference

$$V_{BG} = \frac{E_G(J)}{q(coulomb)}$$

21

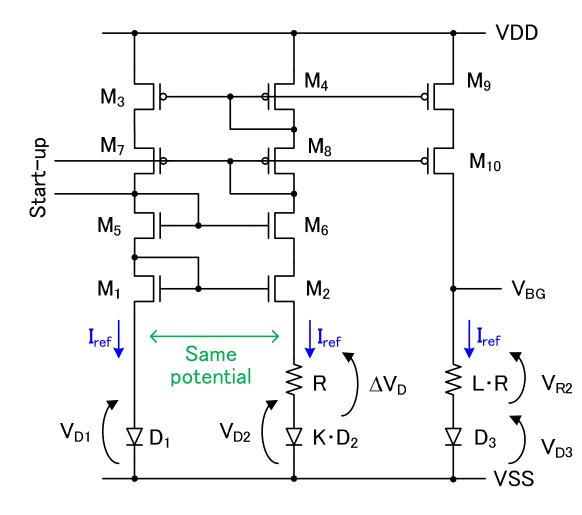

#### Cascode BGR

M4, M3: Current mirror  $V_{GS1} = V_{GS2}$  because  $I_{DS1} = I_{DS2}$ . The source potential of M1 and M2 is same, then  $V_{D1} = V_{D2} + \Delta V_D$

The cascode current mirror can reduce the current error by the residual temperature dependence of  $V_{D3} + V_{R2}$ , but it requires the large supply voltage.

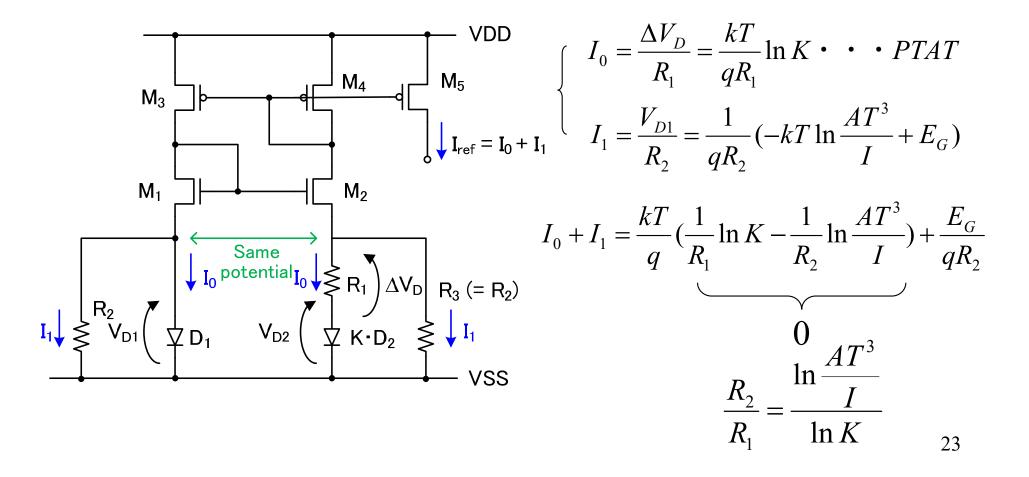

#### BGR current reference

Temperature-independent current reference circuit with BGR

#### Design example of cascode BGR